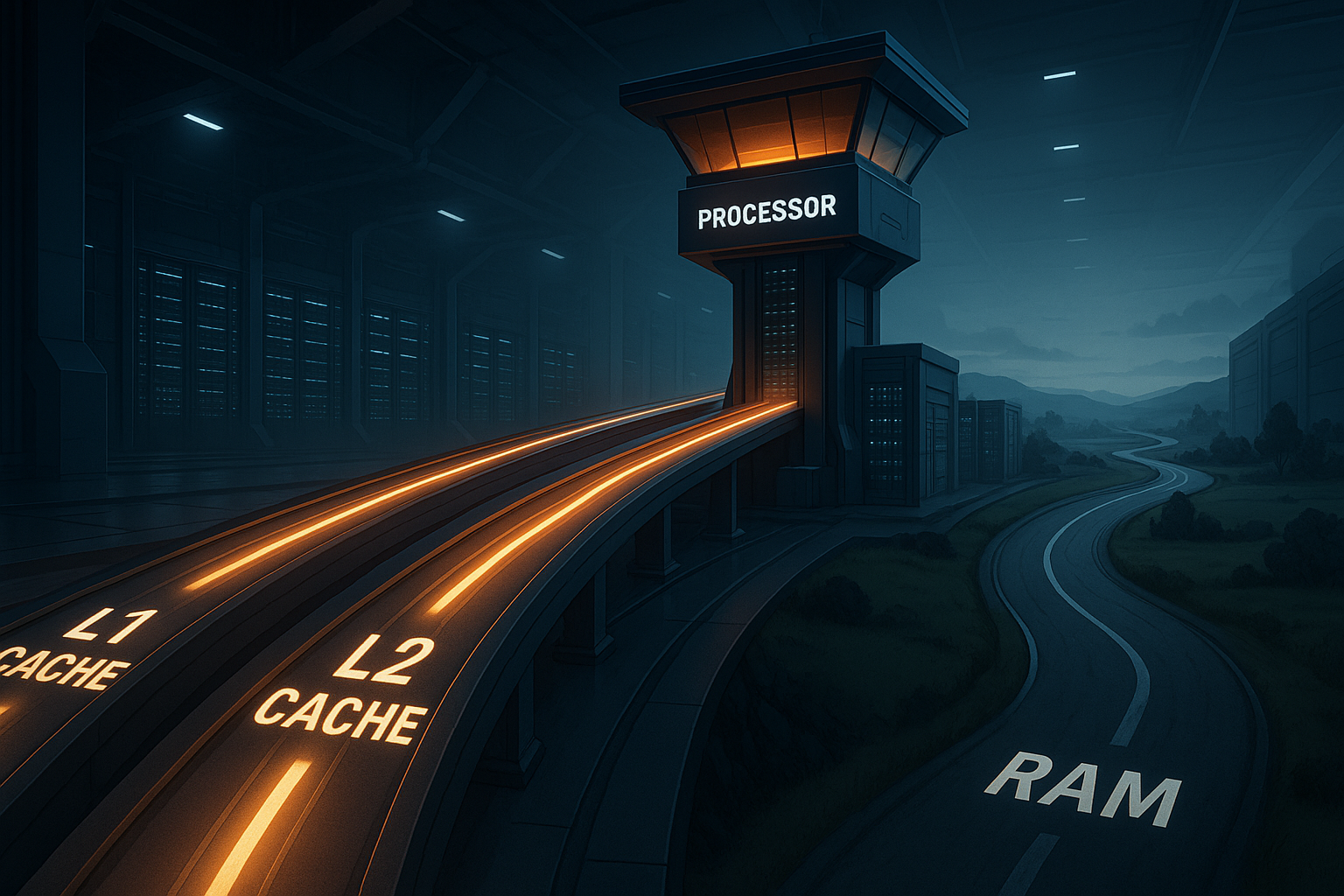

CPU-cache-hosting er afgørende for indlæsningstid og TTFB i mange reelle arbejdsbelastninger, fordi L1–L3-data leveres direkte til kernen på nanosekunder og dermed omgår den langsomme RAM-adgang. Jeg viser tydeligt, hvornår cache-størrelse og -hierarki dominerer beregningstiden, og hvorfor mere RAM uden en stærk cache næppe har nogen effekt.

Centrale punkter

- L1–L3 bufferer hot data tættere på kernen og reducerer latenstiden betydeligt.

- Cache-hierarki slår RAM ved dynamiske forespørgsler og høj parallelitet.

- Cache pr. kerne tæller mere end den rene RAM-mængde hos VPS/DEDI.

- Arbejdsbyrder som WordPress, DB-forespørgsler og PHP drager direkte fordel heraf.

- Valg af tarif med CPU-fokus leverer mærkbart hurtigere svar.

Hvorfor CPU-cache L1–L3 gør hosting mærkbart hurtigere

En Cache sidder direkte på processoren og leverer instruktioner og data uden om hovedkortet. L1 er lille, men ekstremt hurtig; L2 udvider bufferen; L3 holder meget hentbart materiale klar til alle kerner. På den måde undgår processoren ventetider, der opstår ved adgang til RAM opstår. Disse ventetider summeres på webservere, da hver anmodning udløser flere database- og filsystemadgange. I logfiler ser jeg igen og igen, hvordan korte cache-hits erstatter lange RAM-adgange og dermed reducerer TTFB og CPU-udnyttelse.

Sådan fungerer L1, L2 og L3 sammen

L1-cachen leverer instruktioner og data på få taktcyklusser, hvilket Forsinkelse til minimale værdier. Hvis L1 ikke rammer, behandler L2 anmodningen med lidt mere tid. Hvis L2 rammer forbi, træder L3 til, som er forholdsvis stor og holder hitraten høj. Først når L3 rammer forbi, ender CPU'en i RAM, hvilket bremser cyklussen. Jeg planlægger derfor hosting, så der er tilstrækkelig L3 er tilgængelig, fordi netop der er mange parallelle webprocesser, der har adgang til fælles datasæt.

Cache vs. RAM: Taloversigt

Jeg opsummerer de typiske størrelser og relative hastigheder, så Klassificering lettere. Værdierne varierer afhængigt af CPU-generationen, men forholdet forbliver det samme. L1 er meget lille og ekstremt hurtig, L2 ligger i midten, L3 er stor og deles ofte mellem kerner. RAM giver kapacitet, men højere adgangstid og svigter ved tilfældige adgang. Netop disse tilfældige adgang dominerer i webserver-stacks bestående af webserver, PHP og database.

| hukommelsesniveau | Typisk størrelse | Latens (relativ) | Faktor vs. RAM | Delt? |

|---|---|---|---|---|

| L1 (instruktioner/data) | 32–64 KB pr. kerne | ekstremt lav | op til ~170× hurtigere | nej |

| L2 | 256 KB–1 MB pr. kerne | meget lav | Betydeligt hurtigere | nej |

| L3 | op til 40 MB+, delt | lav | op til ~15 gange hurtigere | ofte ja |

| RAM (DDR) | GB-område | høj | Baseline | Systemomfattende |

Cache-arkitektur i detaljer: inklusiv, eksklusiv, chiplets

Ikke alle L3'er er ens: Nogle arkitekturer kører en inklusive L3 (han opbevarer kopier af L1/L2-linjerne), andre satser på eksklusiv/mest eksklusiv (L3 indeholder ekstra linjer, der ikke findes i L1/L2). Inklusiv øger sammenhængen og enkelheden, men koster effektiv plads. Eksklusiv udnytter kapaciteten bedre, men kræver smart offerstyring. I chiplet-baserede designs er L3 ofte pr. Die bundtet; forespørgsler, der lander på en anden, betaler en ekstra latenstid. For hosting betyder det: Jeg prøver at, Arbejdsbelastninger og deres hotsets pr. dag for at samle dem, så størstedelen af adgangen forbliver i det lokale L3. Det reducerer variansen og stabiliserer 95./99. percentilen.

Reelle arbejdsbelastninger: WordPress, databaser, API'er

Dynamiske sider starter mange små Adgange: PHP henter skabeloner, MySQL leverer rækker, webserveren læser filer. Hvis disse mønstre findes i cachen, falder TTFB direkte. WordPress viser dette meget tydeligt, især ved CPU-bundne temaer og mange plugins. Hvis man går dybere ned, finder man typiske flaskehalse i CPU-bundet WordPress beskrevet. Jeg planlægger at bruge kerner med meget L3 pr. kerne, fordi query-hotset og bytecode-fragmenter oftere forbliver i bufferen.

Praktiske værdier: Hotset for en mellemstor WordPress-side ligger ofte i området med et enkeltcifret antal megabyte (Opcache-bytecode, Autoloader-maps, hyppige DB-indekser). E-handelsbutikker bringer desuden pris- og lagerindekser samt sessionsdata i spil. Hvis denne pakke passer ind i L3, reduceres svingningerne i responstiden betydeligt – selv uden ændringer i applikationen eller RAM-størrelsen.

Kerner, tråde og cache pr. kerne

Mange kerner hjælper kun, hvis der er nok pr. kerne Cache står til rådighed, ellers konkurrerer tråde mere. Hyper-Threading fordobler ikke regnekraften, men deler cachestrukturen. Med mere L3 pr. kerne forbliver udnyttelsen stabil og variationen i svartiderne lille. Især multitenant-VPS drager fordel af dette, fordi hotsets fra flere websteder forbliver i den fælles L3. Jeg er derfor opmærksom på forholdet mellem kerner og L3-kapacitet, ikke blot på den rene kerne-tæller.

En almindelig misforståelse: “Flere tråde = større gennemstrømning.” I praksis øges antallet af konflikter og kontekstskift. Jeg begrænser arbejdere nøjagtigt således, at IPC (Instructions per Cycle) forbliver høj, og fejlprocenten ikke løber løbsk. Dette giver ofte bedre percentiler i belastningstests end en tilgang med “maksimal parallelitet”.

NUMA, hukommelsesadgang og latenstid

Moderne servere bruger ofte flere NUMA-knudepunkter, hvilket kan forlænge veje i hukommelsen. Hvis man fordeler processer på tværs af knudepunkter, øger man latenstiden og reducerer cache-hits. Jeg foretrækker at binde tjenester, så hotsets forbliver lokale. Et kort overblik over NUMA-arkitektur viser, hvor vigtig nærheden mellem kerne, cache og RAM-bank er. Med en god placering sikrer forespørgsler mere Cache-hit og mindre dyre udflugter til fjerne destinationer.

Det er vigtigt: Cross-NUMA-trafik er ikke kun et RAM-spørgsmål. L3-koherens over knudepunkter øger også latenstiden. Derfor tester jeg under belastning, på hvilket NUMA-knudepunkt den aktive database og PHP-FPM-puljer ligger, og holder web- og DB-processer så vidt muligt i samme topologi. Dette forhindrer, at sessioner, forespørgselsplaner og bytecode konstant bliver flyttet “over gaden”.

I/O venter på CPU'en: Hvorfor RAM sjældent er flaskehalsen

RAM-kapacitet hjælper med filsystemcachen, men det meste ventetid opstår i applikationens kodesti. Disse stier drager fordel af hurtige instruktions- og datacacher, ikke af flere gigabyte. Ved tilfældige adgangssøgninger forsvinder RAM-båndbredden hurtigt, mens en stor L3 udjævner springene. Jeg måler i profilere, at cache-miss-rater er tæt korreleret med TTFB og 95. percentil. Derfor vægter jeg CPU-cache højere end ren RAM-størrelse, indtil fejlprocenten falder.

SSD'er “virker” også hurtigere, når CPU'en venter mindre. Færre kontekstskift og kortere kodestier betyder, at I/O-færdiggørelse behandles hurtigere. Caches er her katalysatoren: De holder de hotte instruktionsstier varme og minimerer afbrydelser, mens scheduleren skal flytte færre tråde frem og tilbage.

Forstå cache-fejltyper og reducer dem målrettet

I praksis skelner jeg mellem fire årsager:

- Obligatoriske fejl (kold): Første adgang til nye data; kan reduceres ved hjælp af opvarmningsstrategier (forhåndsindlæsning af de mest anvendte ruter, opvarmning til Opcache).

- Kapacitetsmangler: Hotset passer ikke helt ind i Lx; ved hjælp af mindre kodestier, færre plugins og optimerede indekser reducerer jeg størrelsen.

- Konfliktfejl: For mange linjer kortlægges til de samme sæt; bedre datalokalitet og reduceret spredning hjælper, ligesom “glattere” datastrukturer.

- Sammenhængsmangler: Delte data skrives ofte; jeg minimerer globale mutables og bruger lokale caches (APCu) for at dæmpe skrive-trafikken.

På applikationsniveau betyder det, at jeg reducerer tilfældige adgangsforsøg (f.eks. mindre scatter-gather i PHP), samler forespørgsler, holder objektcaches konsistente og sørger for, at hot-code ikke konstant kompileres eller genindlæses.

Praktiske købskriterier for hosting-priser

Ved VPS og dedikerede servere tjekker jeg først CPU-generation, derefter cache-størrelse pr. kerne. En tarif med mindre RAM, men stærk L3 pr. kerne slår ofte en model med meget RAM og svag cache. Også vigtige faktorer er clockfrekvens under belastning, turbo-adfærd og hvordan udbyderen fordeler kerner. For butikker med mange samtidige forespørgsler betaler L3-kapacitet sig overproportionalt. Hvis du alligevel bruger cache i app, DB og CDN, får du yderligere fordel af en Cache-stærk CPU, fordi hotsets rammer oftere.

Jeg spørger eksplicit: Hvor mange vCPU'er pr. fysisk kerne deler udbyderen? Blendes vCPU'er på tværs af NUMA-grænser? Er der garantier for, at vCPU'er ligger inden for samme dies? Sådanne detaljer afgør, om L3 fungerer som accelerator eller som noisy neighbors. fortyndet vil.

Tuning: Software udnytter cachen bedre

Jeg holder PHP‑Opcache, JIT‑indstillinger og DB‑Buffer sådan, at hotpfade i L3 passer og re-kompileringer er sjældne. For hård thread-pinning hæmmer scheduler-optimeringer; hvorfor det ofte ikke nytter meget, viser CPU-pinning. I stedet begrænser jeg arbejdere, så de ikke fortrænger cachen. Jeg sørger for korte kodestier, færre forgreninger og varme bytecode-cacher. Det reducerer fejlprocenten, og processoren bruger mere tid på nyttig arbejde i stedet for at vente.

Levering i PHP-stakke OPcache-hukommelse og interne strenge markant bedre beliggenhed. Derudover satser jeg på en lokal APCu til læseintensive data og en persistent objektcache (f.eks. Redis) med et overskueligt antal nøgler, så hotkeys forbliver i L3. I databasen reducerer jeg sekundære indekser til det nødvendige og optimerer sorteringsrækkefølgen, så der opstår sekvenser i stedet for springmønstre.

Måleparametre: Hvad jeg overvåger

Jeg observerer konstant Miss-rater (L1/L2/L3), IPC (Instructions per Cycle) og takt under belastning. Derudover kontrollerer jeg TTFB, 95./99. percentil og fejllogfiler ved belastningsskift. Disse nøgletal viser, om kodestien passer ind i cachen eller glider væk. Jeg korrelerer fejlspidser med implementeringer, trafikspidser og nye plugins. På den måde finder jeg hurtigt de steder, hvor der er behov for mere Cache-hit give størst mulig nytte.

For ad hoc-analyser ser jeg live på “perf stat”‑Metrikker som cykler, instruktioner, forgreninger, forgreningsfejl og LLC-fejl. Jeg bruger konstant registreringer, frekvens under belastning (turbostat) og kontekstskift pr. sekund. Når IPC falder under pres og LLC-fejl stiger samtidigt, er flaskehalsen næsten altid cachekapacitet eller datalokalitet – ikke RAM-throughput.

Benchmarking og testopbygning: måling af realistiske svar

Jeg tester med repræsentative ruter i stedet for kun statiske filer. En blanding af startside, produktdetaljer, søgning og checkout dækker forskellige kodestier. Med differentierede belastningsniveauer (kold, varm, hed) kan jeg se, hvor hurtigt cachen fyldes, og hvor den tipper. Det vigtige er Steady-state-fase, hvor frekvens, IPC og fejlrate kører stabilt. Først her sammenligner jeg takster og CPU-generationer på en fair måde.

Målbare signaler:

- TTFB-median falder markant efter opvarmning og forbliver lav → Caches virker.

- 95./99. percentil afviger kun lidt ved spidsbelastning → tilstrækkelig L3 pr. kerne.

- IPC stiger med færre arbejdere → konflikter og fejl falder.

- LLC-fejl korrelerer med nye plugins/funktioner → Hotset forstørret.

For hver test dokumenterer jeg den aktive CPU-frekvens, antallet af arbejdere, ruteblandingen og, hvis relevant, NUMA-placeringen. På den måde kan optimeringer entydigt tilordnes og reproduceres.

Virtualisering og multitenancy: Del cache uden at miste den

I VPS-miljøer deler kunder den samme fysiske L3. Hvis en gæsts vCPU'er er bredt fordelt over maskinen, mister man lokalitet. Gode udbydere samler en gæsts vCPU'er på samme CCX/CCD/Tile. Det ser jeg i form af mere stabile percentiler og mindre varians. Derudover begrænser jeg arbejdere, så min egen stack ikke oversvømmer L3 og kommer i konflikt med naboer.

Containere på samme host konkurrerer på samme måde. En slank basiscontainer med forvarmet Opcache og så lidt dynamisk autoloading som muligt holder L3 ren. Jeg undgår aggressive sidecars på samme node, der producerer store instruktionsarealer (f.eks. “log alt, overalt”). Det hører hjemme på en separat node eller uden for hot path-CPU'en.

Prefetcher, TLB og sidestørrelser: skjulte løftestænger

Moderne CPU'er har Prefetcher, der foretrækker lineære mønstre. Jo mere sekventielt kode og data er arrangeret, jo større er fordelen. Derfor foretrækker jeg strukturerede arrays og mere kompakte strukturer frem for hash-tunge og stærkt forgrenede layouts. Desuden er jeg opmærksom på TLB (Translation Lookaside Buffer): Mange side-walks er dyre og trækker L1/L2 med. Store sidestørrelser (Huge Pages) kan hjælpe med at dække bytecode- og DB-hotsets med færre TLB-poster. I InnoDB- og JIT-konfigurationer tjekker jeg derfor, om større sider giver målbare fordele – altid med A/B-måling, da ikke alle stakke drager samme fordel.

Praksis-tjekliste: hurtig cache-hosting i 10 trin

- CPU-generation og L3 pr. kerne Kontroller ikke kun CPU-tal og RAM.

- Forespørg om vCPU-allokering: bundling pro Die/NUMA i stedet for spredning.

- Begræns arbejdere til IPC-sweetspot; minimer variansen i percentilerne.

- Dimension PHP-Opcache generøst, men målrettet; undgå re-kompilering.

- Brug vedvarende objektcacher, hold nøglepladsen slank.

- Skræddersy DB-indekser til varme forespørgsler; reducer tilfældig adgang.

- Sørg for NUMA-lokalitet: Web, PHP, DB i samme node, hvor det er muligt.

- Prefetcher-venlige datastier: mere sekventielle, færre spring.

- Sørg for udrulning med opvarmning; opfang kolde fejl, før trafikken topper.

- Overvågning: IPC, L1/L2/L3-missrate, cyklus, 95./99. percentil kontinuerlig korrelation.

Kort opsummeret

I hosting er en stærk CPU-cache L1-L3 prioriterer alle dynamiske forespørgsler, mens ekstra RAM primært giver kapacitet. Jeg prioriterer derfor cache-størrelse pr. kerne, ren procesplacering og passende antal arbejdere. I værktøjer kan jeg se, at færre misses giver målbart bedre svartider og stabile percentiler. Når du vælger tariffer, skal du være opmærksom på cachespecifikationer og CPU-generation, ikke kun GB-specifikationer. Sådan får du mere ud af den samme software Strøm ud - uden dyre hardwareopgraderinger.